RISC-V ISA Vector Extension

Vector Extension

ref

Vector extension manual

RISC-V Vector Extension学习笔记

https://zhuanlan.zhihu.com/p/140772040

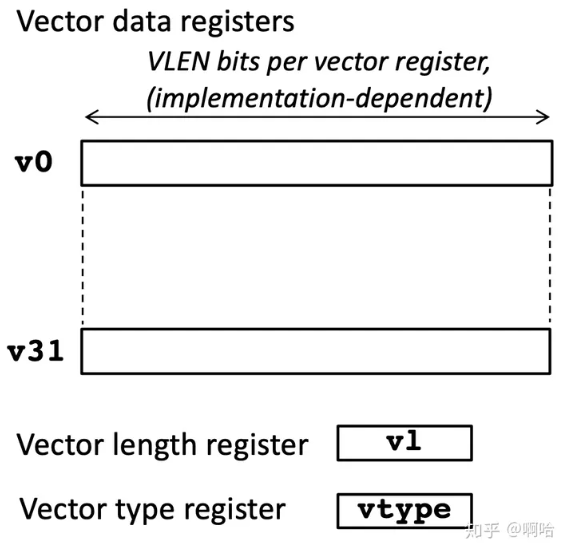

additional state

- 32 vector register, v0-v31, each lenght is VLEN

- VLEN decided by implementor

- must be power of 2

- vl

- vector length register

- not to be comfused with VLEN

- 說明多少個向量中的多少個元素會被運算

- vlmax(sew, lmul) = (VLEN / sew) * lmul

- vtype

- vector type

- vector type

vector type register

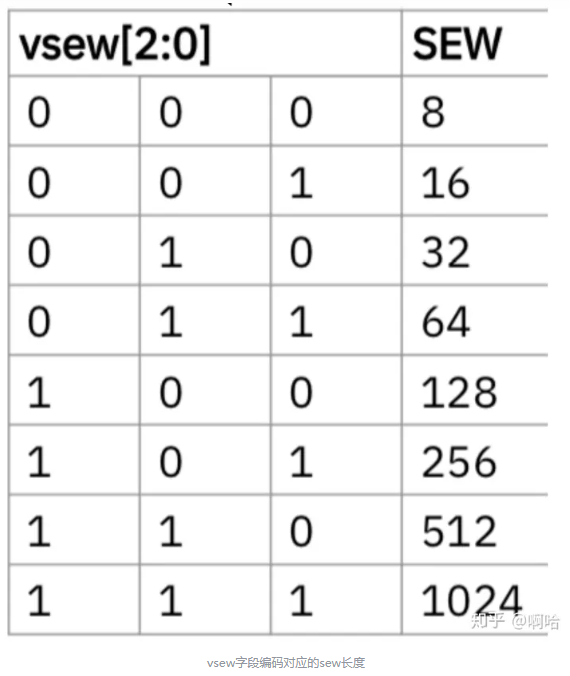

- vsew[2:0]:用于编码向量的标准元素宽度(SEW)

- 向量暫存器中一個元素的寬度

- vlmul[1:0]:用于编码向量寄存器长度multiplier(LMUL=

=1-8) - 当vlmul为2时,表示一条指令可以同时操作两个向量寄存器

- 當vlmul小於1的時候,代表只使用一部份的register做運算

- vediv[1:0]:用于编码向量元素被划分到相等的子元素的方式(EDIV=

=1-8)

vector operation

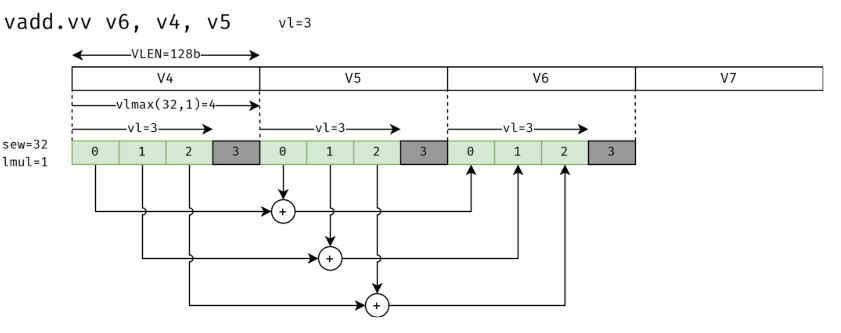

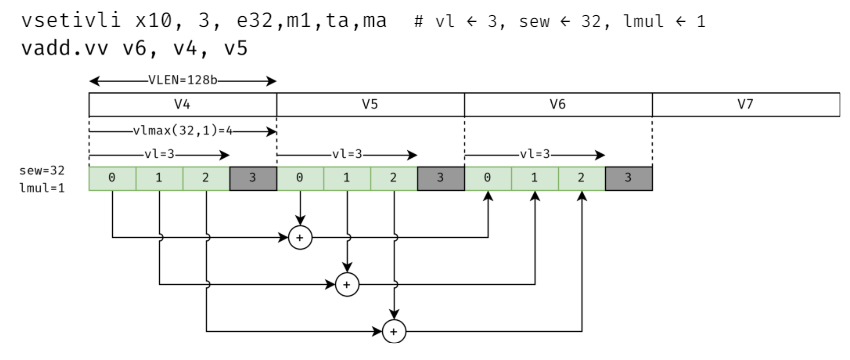

- when vl < vlmax

- there are ele. that are not operate, called tail ele.

- RVV offers 2 policies

- tail undisturbed: 保留不動

- tail agnostic: 可以如上,也可以全部設為1

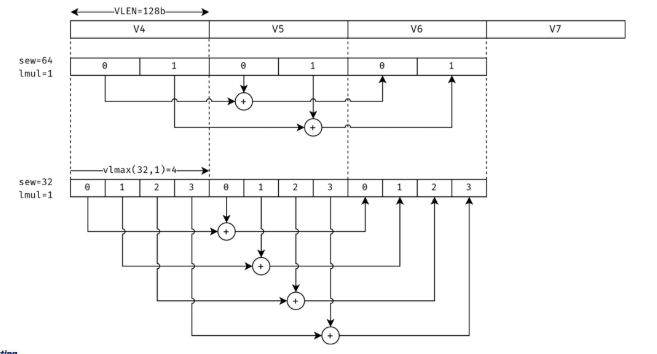

Ex 5

vadd.vv v6, v4, v5 //vl = vmax

Ex 6

vadd.vv v6, v4, v5 //vl = 3

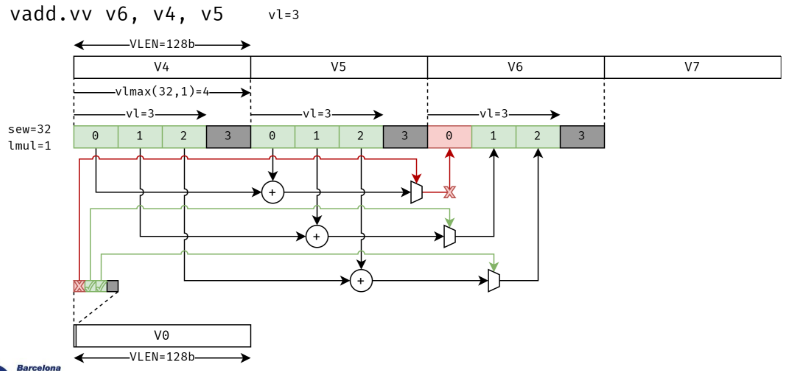

Masking(Prediction)

可以使用一個v register作為mask擋掉某些bit的設置

- 一般使用v0

- 以single bit作為單位

ex.

non-tail ele.

- 由mask決定是否為active or inactive

- inactive同樣有兩個policies

- 跟tail的規則一樣

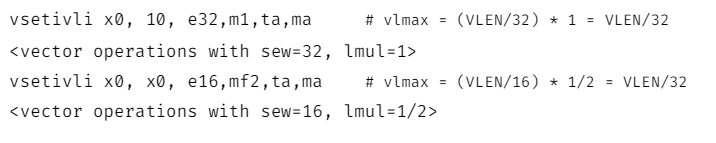

Setting vl and vtype

using

- vsetvl / vsetvli / vsetivli inst.

- vle*ff inst.

the most common is vsetvli

- vsetvli rd, rs, eN, mX, tP, mP

- rd: updates with the vector length computed

- rs: input register that contains AVL

- 代表接下來程式要使用的向量長度

- vl

- eN: N, which is sew

- mX: X, which is lmul

- tP: P, policies of tail

- a or u

- mP: P, policies of mask

- vsetivli

- replace rs as immediate

Ex.

special case

- vsetvli rd, x0, eN, mX, tP, mP //rd != x0

- sets vl to vlmax

- vsetvli x0, x0, eN, mX, tP, mP

- only changes vtype

- only vaild when the new vlmax is left unchanged

if AVL > vlmax

- 會自動壓縮到小於vlmax

- 寫的時候,要確保AVL < vlmax

- 否則會出現難以預測的問題

RISC-V ISA Vector Extension

https://z-hwa.github.io/webHome/[object Object]/Computer Organization/RISC-V ISA Vector Extension/